1681

2021-12-03

1681

2021-12-03

颗粒在线讯:铁电晶体管(FeFET)具有非易失性数据存储、纳秒级的编程/擦除速度、低功耗操作、超长的数据保存时间以及与CMOS工艺兼容等优点,被认为是未来非易失存储器应用的候选器件。在5nm技术节点以下,由于器件栅长(小于18纳米)和铁电薄膜厚度(大约10纳米)相近,基于FinFET和水平环栅晶体管(GAAFET)的FeFET无法进一步微缩,而垂直环栅晶体管(VGAAFET)不受栅长的约束,同时在3D集成和布线上有明显优势,具有大幅增加集成度的潜力,因此更适合5纳米技术节点以下的FeFET结构。

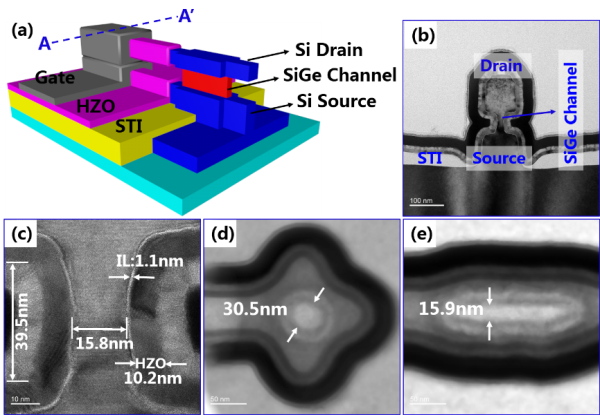

中国科学院微电子研究所集成电路先导工艺研发中心研究员朱慧珑团队利用自主研发的集成工艺,制造出了具有自对准栅极的铁电垂直环栅纳米晶体管(Fe-VSAFET),其中包括栅长为40纳米,沟道厚度为16纳米的纳米片和直径为30纳米的纳米线两类器件。该器件具有小于pA级的漏电,大于107的开关比,100ns级的编程/擦除速度和2.3V的最大存储窗口等优异的电学特性,并且制程工艺与主流CMOS兼容。

该成果近日发表在IEEE Electron Device Letters上(DOI: 10.1109/LED.2021.3126771)。该研究得到中科院战略性先导科技专项预研项目和微电子所所长基金项目资助。

(a)Fe-VSAFET器件结构图;(b)-(e)Fe-VSAFET的TEM顶视和截面图

上一篇: 重庆研究院污水处理新型工艺研究取得进展

版权与免责声明:

(1) 凡本网注明"来源:颗粒在线"的所有作品,版权均属于颗粒在线,未经本网授权不得转载、摘编或利用其它方式使用上述作品。已获本网授权的作品,应在授权范围内使用,并注明"来源:颗粒在线"。违反上述声明者,本网将追究相关法律责任。

(2)本网凡注明"来源:xxx(非颗粒在线)"的作品,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责,且不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网下载使用,必须保留本网注明的"稿件来源",并自负版权等法律责任。

(3)如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。